Global SIPI University

Global Signal Integrity and Power Integrity (SIPI) University

Tuesday – Wednesday – Thursday, August 19 – 21, 2025

Room 202

Fee: $295 Advance/ $345 Regular

5-Day Symposium registration is required in addition to the Global SIPI fee.

The Organizing Committee of the 2025 IEEE International Symposium on Electromagnetic Compatibility and Signal & Power Integrity (EMC+SIPI) is planning to offer a high-quality educational event encompassing Signal Integrity (SI) and Power Integrity (PI): the Global Signal Integrity and Power Integrity University.

Similar to the Clayton R. Paul Global EMC University that is held annually during the International Symposium, the intent is to offer two full days of lectures carefully curated to cover basic and advanced concepts of SI & PI during the symposium week. SI & PI are gaining ever-growing attention due to the higher data rates and larger currents in modern high-speed digital systems. Industry requires skilled engineers with a background in these two disciplines to address the increasing complexity and challenges of electronic system design.

The IEEE EMC Society therefore decided to offer – after its introduction in 2024 at the Symposium in Phoenix, Arizona – two full days of courses during the EMC + SIPI Symposium 2025 to bridge this gap. The mission of the Global SIPI University will be to give students, technicians, and engineers the opportunity to acquire SI & PI skills directly from experienced and well-known instructors from both industry and academia.

This year the program extends to 2 days to offer both lectures and practical demonstrations. The intent is to expand the discussion on the background concepts and to provide a more detailed presentation of advanced methods for achieving the current design challenges. Moreover, the demos will encompass the use of instruments typically employed for analysis, measurement and troubleshooting for the signal and power integrity.

MEET OUR CO-CHAIRS

Christian Schuster, Hamburg University of Technology, Germany (IEEE Fellow)

Christian Schuster received a Diploma degree in physics in 1996 and a Ph. D. degree in electrical engineering in 2000. Since 2006 he is a full professor at Hamburg University of Technology (TUHH), Germany. Prior to TUHH he was with the IBM T. J. Watson Research Center, Yorktown Heights, NY. His interests include signal and power integrity of digital systems, multiport measurement and calibration techniques, and development of physics-based as well as data-based modeling, simulation and optimization methods for EMC+SIPI. In the recent past, he has served as an Associate Editor for the IEEE Transactions on EMC, as an Adjunct Associate Professor at the School of

Electrical and Computer Engineering of the Georgia Institute of Technology, and as the President of the NIT Northern School of

Technology Management at TUHH.

Francesco de Paulis, University of L’Aquila, L’Aquila, Italy

Francesco de Paulis received the M.S. degree in Electrical Engineering in May 2008 from Missouri University of Science and Technology (formerly University of Missouri-Rolla), USA, and the PhD degree in Electrical and Information Engineering in 2012 from the University of L’Aquila, L’Aquila, Italy. He is currently an Associate Professor at the Electromagnetic Compatibility and Signal Integrity Laboratory, University of L’Aquila, Italy, and an Adjunct Professor at the Missouri University of Science and Technology. His main research interests are in signal and power integrity, high speed channel design, electromagnetic compatibility, antenna design and measurement techniques, design of electronic devices and systems for space applications.

MEET OUR INSTRUCTORS

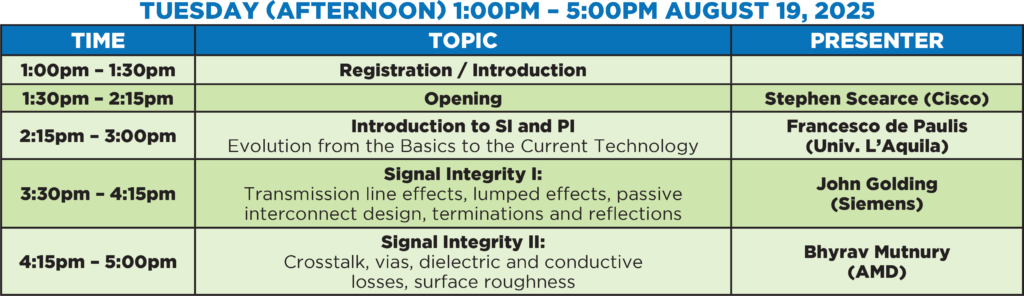

Tuesday, August 19th

Stephen Scearce, Cisco

Apex, NC, USA

Opening Session: Real world challenges for Signal and Power Integrity

Abstract

This introductory session delves into the heightened scrutiny required for SI/PI design, simulation, and implementation in our newest systems. It highlights the complexities faced in our High-Speed Serdes design at 56-224 Gbps, addresses critical issues in DDR5 for 6400/8400MTs implementation, and explores difficulties in distributing 1-2kW of power to our latest ICs. Highlighting these challenges and potential solutions establishes the foundation for the exciting content of the SI-PI Global University

About Stephen Scearce

Stephen Scearce is a Hardware Engineering Director of Cisco/Meraki’s Electronics Packaging and Diagnostics team. Stephen provides the technical direction/leadership for Signal Integrity, Power Integrity, Mechanical/Thermal Design, ECAD, and Software Diagnostics design in US/China. Stephen has worked for Cisco for 24 years focused on ASIC/System PI, SI, Package Design, and EMC design. He holds 13 issued patents and has co-authored 17 papers. He has volunteered for the IEEE Electromagnetic Compatibility Society for the past 11 years and is currently serving as the Society Treasurer (2023-2026), and the 2025 EMC+SIPI Symposium Vice Chair. Stephen received his BSET and MSEE from Old Dominion University, Norfolk VA.

Francesco de Paulis, University of L’Aquila

L’Aquila, Italy

Introduction to SI and PI: Evolution from the Basics to the Current Technology

Abstract

This presentation will introduce the concepts of signal and power integrity, and the evolution, in the past two decades, of the challenges associated with the modeling, analysis, and design of high speed interconnects and high-current PDNs. An overview of the current trends based on the state of the art of the technology discussed in the following sessions will be given.

About Francesco de Paulis

Francesco de Paulis received the M.S. degree in Electrical Engineering in May 2008 from Missouri University of Science and Technology (formerly University of Missouri-Rolla), USA, and the PhD degree in Electrical and Information Engineering in 2012 from the University of L’Aquila, L’Aquila, Italy. He is currently an Associate Professor at the Electromagnetic Compatibility and Signal Integrity Laboratory, University of L’Aquila, Italy, and an Adjunct Professor at the Missouri University of Science and Technology. His main research interests are in signal and power integrity, high speed channel design, electromagnetic compatibility, antenna design and measurement techniques, design of electronic devices and systems for space applications.

John Golding, Siemens EDA

Livonia, MI, USA

Signal Integrity I: Transmission line effects, lumped effects, passive interconnect design, terminations and reflections

Abstract

In this session we will discuss signal integrity effects and design considerations of passive interconnects. Understanding the effects channels have on signals is critical to designing for signal integrity, and designing for signal integrity is critical for product design. Concepts including lumped and transmission line effects, reflections, and terminations will be presented and illustrated with examples. A grasp of these fundamental concepts enables engineers to solve many signal integrity challenges and is a foundation for learning additional, and more advanced topics in signal integrity.

About John Golding

John Golding is a Senior Applications Engineer Consultant with Siemens EDA. He has been working with engineers in several industries for over 10 years to solve their Signal and Power Integrity analysis challenges. Prior to his current role, he was a hardware engineer for 18 years where he responsible for the design, analysis, and verification of high-speed communications products. He holds a BSEE degree from the University of Michigan and a MSEE degree from Illinois Tech.

Bhyrav Mutnury, AMD

Austin, TX, USA

Signal Integrity II: High-speed signal integrity challenges and opportunities

Abstract

The challenges associated with high-speed signal integrity (SI) are becoming exponentially complex with the doubling of signal speeds every generation. As the signal speeds go from 64-224 Gbps, a new plethora of passive interconnect impairments need to be carefully analyzed. In this presentation, SI design challenges and opportunities are discussed using real design examples. The presentation covers SI impairments due to crosstalk, reflections and attenuation coming from passive channels in high-speed designs.

About Bhyrav Mutnury

Bhyrav Mutnury is a Senior Fellow at AMD, part of Technology and Engineering division where he is responsible for designing next generation high-speed interfaces. Prior to this, Dr. Mutnury was a Senior Distinguished Engineer and Global Team Leader of Signal Integrity group at Dell Technologies. Dr. Mutnury has co-advised 5 PhD students and currently co-advising 2 PhD students. He received his Doctor of Philosophy degree in Electrical Engineering in 2005 from the Georgia Institute of Technology, Atlanta, GA. Dr. Mutnury has authored more than 100 publications in various conferences and journals. Dr. Mutnury has 250 issued patents and another 50 in the pipeline. He is currently an IEEE Fellow and the recipient of IEEE Technical Achievement Award.

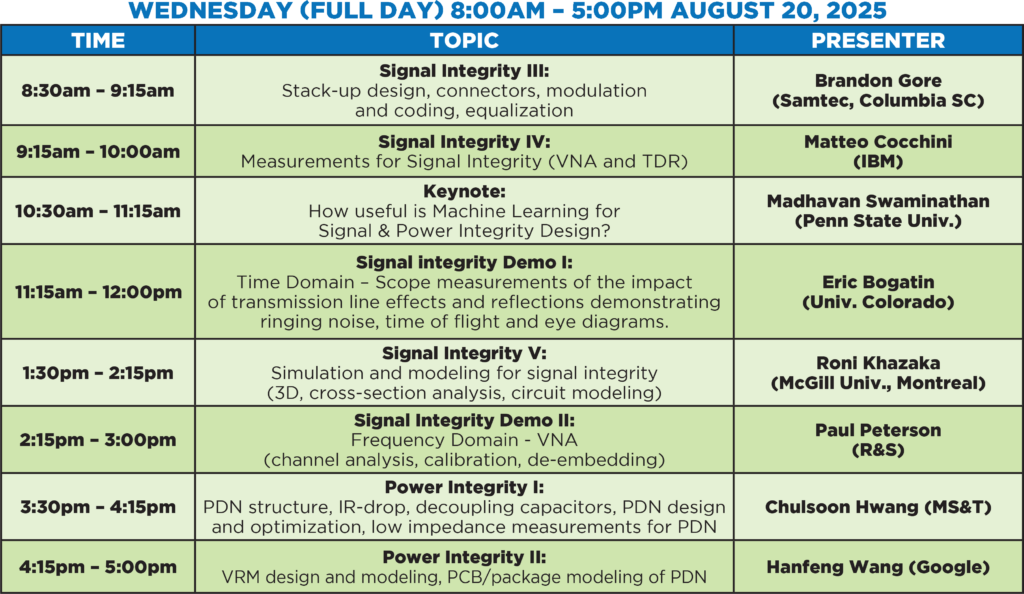

Wednesday, August 20th

Brandon T. Gore, Samtec

Columbia, SC, USA

Signal Integrity III: Stack-up design, connectors, modulation and coding, equalization

Abstract

The latest trends in SI design require an understanding from basic interconnect design challenges through to how the DSP receivers correct interconnect distortions. PCB stackup design choices have tradeoffs that impact loss, routing density, and vertical transitions. These vertical transitions, especially, have negative impacts on the breakout region (BOR) connector performance targets that go along with mechanical requirements for mating of the connector. However, signaling is ultimately in the time domain, and it can be helpful to use single bit responses of the channel to understand the limits of equalization on ISI. Additionally, modulation choices such as Pulse Amplitude (PAM4 or PAM6) tighten the requirements on SNR. The presentation introduces the above subjects, and it shares tips specific to the design of interconnect component evaluation for 224 Gb/s signaling.

About Brandon T. Gore

Brandon T. Gore is presently a Principal Technologist at Samtec managing both the Signal Integrity R&D and Electronic Industry Standards teams. His research focuses are advanced interconnect materials, glass packaging, direct drive optics, and general signal integrity bottlenecks for beyond 200Gbps data rates. He is an active contributor to both IEEE 802.3 and OIF Common Electrical I/O projects. Brandon received the PhD degree in electrical engineering from the University of South Carolina under Dr. Paul G. Huray.

Matteo Cocchini, IBM

Poughkeepsie, NY, USA

Signal Integrity IV: Measurements for Signal Integrity (VNA and TDR)

Abstract

This lecture aims to provide a comprehensive introduction to the fundamental principles behind Vector Network Analyzer (VNA) and Time Domain Reflectometer (TDR) measurements. The session will begin by covering the core theoretical concepts that support these instruments, followed by illustrative practical examples based on real designs.

For the VNA, in addition to the standard extraction of S-parameters, the discussion will emphasize advanced techniques, such as calibration processes, embedding and de-embedding methods, and the presentation of real-world data. Meanwhile, the TDR portion of the lecture will delve into its essential principles, explore its common industrial applications, and address frequent challenges and potential issues that SI engineers could encounter in test environments.

About Matteo Cocchini

Matteo Cocchini received his Laurea in Electronic Engineering in June 2006 from University of L’Aquila, L’Aquila, Italy. He received the Master of Science in Electrical Engineering from Missouri University of Science and Technology, Rolla, MO in May 2008. He is an IBM Master Inventor and a senior engineer, team leader of the IBM Z I/O signal and power integrity engineering team, Poughkeepsie, New York.

Madhavan Swaminathan, The Pennsylvania State University

State College, PA, USA

Keynote: How useful is Machine Learning for Signal & Power Integrity Design?

Abstract

Design for Signal and Power Integrity has made tremendous progress over the last three decades thanks mainly to the modeling and measurement methods developed and the knowledge base derived from it. Over the last several years the SI/PI community has been focusing on applying machine learning (ML) methods to speed-up computations and ease the design process. But how useful has ML been in the domain of signal and power integrity?

This presentation will cover several ML based approaches applied for SIPI design highlighting the insights gained and future directions in this area.

About Madhavan Swaminathan

Madhavan Swaminathan is the Department Head of Electrical Engineering and is the William E. Leonhard Endowed Chair at Penn State University. He also serves as the Director for the Center for Heterogeneous Integration of Micro Electronic Systems (CHIMES), an SRC JUMP 2.0 Center www.chimes.psu.edu.

Prior to joining Penn State, he was the John Pippin Chair in Microsystems Packaging & Electromagnetics in the School of Electrical and Computer Engineering (ECE), Professor in ECE with a joint appointment in the School of Materials Science and Engineering (MSE), and Director of the 3D Systems Packaging Research Center (PRC), Georgia Tech (GT). Prior to GT, he was with IBM working on packaging for supercomputers.

He is the author of 650+ refereed technical publications and holds 31 patents. He is the primary author and co-editor of 3 books and 5 book chapters, founder and co-founder of two start-up companies, and founder of the IEEE Conference on Electrical Design of Advanced Packaging and Systems (EDAPS), a premier conference sponsored by the IEEE Electronics Packaging Society (EPS). He is a Fellow of IEEE, Fellow of the National Academy of Inventors (NAI), Fellow of Asia-Pacific Artificial Intelligence Association (AAIA), and has served as the Distinguished Lecturer for the IEEE Electromagnetic Compatibility (EMC) society. He has been recognized through many awards with the most recent one being the 2024 IEEE Rao R. Tummala Electronics Packaging Award (technical field award) for contributions to semiconductor packaging and system integration technologies that improve the performance, efficiency, and capabilities of electronic systems.

He received his MS and PhD degrees in Electrical Engineering from Syracuse University, USA.

Eric Bogatin, University of Colorado

Boulder, CO, USA

Signal Integrity Demo I: Time Domain – Scope measurements of the impact of transmission line effects and reflections demonstrating ringing noise, time of flight and eye diagrams

Abstract

All interconnects are transmission lines. We hear about their properties and simulate their effects in various EM or circuit simulator tools. In this demonstration, you will see the impact of transmission line properties. We will use both a low-cost scope and low-cost TDR to show five examples of important properties of transmission lines in the real world. The test boards we will measure are commercially available open-source boards available to anyone. Using these tools and methods, you can replicate these measurements at your facility. These demonstrations include: the time of flight of signals, the instantaneous impedance and reflections with a TDR, how to reduce reflections in scope measurements and measuring the output impedance of a driver using a scope.

About Eric Bogatin

Eric received his BS in Physics from MIT in 1976 and PhD in Physics from the University of Arizona in 1980. He has been active in the SI field for 40 years and has written 15 books and hundreds of articles in this field. Currently, he teaches SI and Electronics courses for undergraduate and graduate students. He is also a Fellow with Teledyne LeCroy and the technical editor of the Signal Integrity Journal.

Roni Khazaka, McGill University

Montreal, QC, Canada

Signal Integrity V: Simulation and Modeling for Signal Integrity

Abstract

Signal and power integrity (SIPI) is one of the main design bottlenecks affecting system performance. As a result, SIPI analysis must also be a core components of electronic design automation (EDA) tools. However, in addition to being a design bottleneck, they also present significant challenges to simulation and design automation tools. In this presentation we focus on the difficulties of integrating interconnect models of varying levels of complexity in the framework of a SPICE like simulators. We present the fundamental reasons why this results in a simulation bottleneck, and some of the established and state of the art methods for addressing this problem.

About Roni Khazaka

Prof. Roni Khazaka received his Bachelor, Master, and Ph.D. degrees in Electrical Engineering from Carleton University, Ottawa, Canada in 1995, 1998, and 2002, respectively. In 2002, he joined the Department of Electrical and Computer Engineering at McGill University, Montreal, QC, Canada, where he currently is an Associate Professor in the department of Electrical and Computer Engineering, and Associate Dean, Academic Program, in the Faculty of Engineering. Prof. Khazaka is a senior member of the IEEE. In 2009, he was a Visiting Research Fellow with the University of Shizuoka, Shizuoka, Japan. In 2017, he was a Visiting Researcher with the Politecnico di Torino, Turin, Italy. He has authored over 100 journal and conference articles in the areas of signal and power integrity, model order reduction, macromodeling and high frequency circuit simulations. His current research interests include signal and power integrity, electronic design automation, numerical algorithms and techniques, the analysis and simulation of RF ICs, and high-speed interconnects and packages.

Paul Peterson, Rohde & Schwarz

Dallas, TX, USA

Signal Integrity Demo II: Frequency Domain – VNA

Abstract

This presentation offers a live demonstration of measuring signal integrity in the frequency domain using a Vector Network Analyzer (VNA), a critical tool for evaluating high-speed communication systems. Focusing on channel analysis, the session will explore practical techniques for assessing signal performance, including impedance, insertion loss, and return loss. Attendees will gain insights into the importance of calibration to ensure measurement accuracy and the process of de-embedding to isolate device-under-test characteristics from fixture effects. Through real-time examples, we will illustrate how VNAs enable engineers to identify and mitigate signal degradation in modern interconnects. This demonstration aims to bridge theoretical concepts with hands-on application, equipping participants with actionable knowledge for optimizing signal integrity in their designs. The session is tailored for engineers and researchers navigating the challenges of power and signal integrity in advanced electronic systems.

About Paul Peterson

Paul Peterson is a VNA Product Planning Engineer within the R&D department at Rohde & Schwarz, bringing a wealth of expertise garnered from his extensive experience in the telecom, defense, and semiconductor design industries. Prior to his current role, he spent over six years providing comprehensive support for the entire range of RF products at Rohde & Schwarz. During that time as an application engineer he used his ability to distill complex technologies into accessible insights. Mr. Peterson frequently engages with large, diverse groups through keynote presentations and in-depth training sessions. As a member of the forward-looking planning team, Mr. Peterson is now responsible for aligning Rohde & Schwarz’s VNA platforms with the evolving needs of both current and future customers.

Chulsoon Hwang, Missouri University of Science and Technology

Rolla, MO, USA

Power Integrity I: PDN structure, IR-drop, decoupling capacitors, PDN design and optimization, low impedance measurements for PDN

Abstract

A Power Distribution Network (PDN) plays a crucial role in delivering stable voltage and minimizing noise in high-speed electronic circuits. Decoupling capacitors are essential components in a PDN, but their effectiveness is impacted by parasitic elements. Proper placement of decoupling capacitors is critical and depends on both the PCB stack-up and the target frequency. This session explores these fundamental concepts, providing guidelines for selecting and placing decoupling capacitors for optimal performance.

About Chulsoon Hwang

Chulsoon Hwang is an Associate Professor at Missouri S&T. Before joining Missouri S&T in 2015, he worked at Samsung Electronics. His research focuses on signal/power integrity, RF/digital integration (RF desensitization), and machine learning-driven hardware design. He has authored or co-authored over 150 papers and has been a co-recipient of more than 10 Best Paper and Best Student Paper Awards at conferences such as IEEE EMC+SIPI, AP-EMC, and DesignCon.

Hanfeng Wang, Google

San Jose, CA, USA

Power Integrity II: VRM design and modeling, PCB/packaging modeling of PDN

Abstract

This presentation will delve into the critical aspects of Power Distribution Network (PDN) modeling and simulation at the system level, focusing on achieving robust power integrity in complex electronic systems. We will begin by exploring the accurate and efficient modeling of Voltage Regulator Modules (VRMs), which are essential for providing accurate prediction of the low-frequency overshoot and undershoot of the transient response of the high di/dt current profile from the System on a Chip (SoC). Subsequently, we will address the intricacies of passive PDN network modeling on Printed Circuit Boards (PCBs). A significant portion of the talk will be dedicated to the automation of key simulation processes. Specifically, we will provide an overview of automated AC impedance simulations, which are vital for understanding the frequency-dependent behavior of the PDN and identifying potential excessive loop inductance from the decoupling caps to the SoC balls. Furthermore, we will examine the automation of DC IR drop simulations, enabling efficient analysis of voltage drops and current distribution across the PCB. This automation aims to significantly reduce manual effort and improve the accuracy and speed of PDN analysis.

About Hanfeng Wang

Hanfeng Wang received the B.S. and M.S. degrees in electronic engineering from Tsinghua University, Beijing, China, in 2005 and 2008, respectively, and the Ph.D degree in electrical engineering from Missouri University of Science and Technology (formerly University of Missouri-Rolla), Rolla, USA, in 2012. From 2012 to 2015, he was a Signal Integrity Engineer with Apple. From June 2015 to July 2017, he joined Microsoft as a Senior Electrical Engineer and since July 2017, he has been the Signal Integrity Engineer and team lead in Google’s Pixel phone division. His current research interests include signal integrity, power integrity, and electromagnetic interference in high-speed digital systems. He is an active Senior member of IEEE and was the chair for TC10 (focusing on signal and power integrity) of the IEEE EMC Society.

Thursday, August 21st

Zhiping Yang, PCB Automation, Inc.

Campbell, CA, USA

Power Integrity III: Package and IC PDN, on-chip VRM

Abstract

This technical talk explores advanced power generation and delivery strategies for data centers, emphasizing emerging techniques such as embedding, vertical power delivery, and Integrated Voltage Regulators (IVRs) implemented at the module, PCB, package, and die levels. The discussion begins by highlighting current trends and pressing challenges in powering AI/ML workloads, including ±400V DC distribution, extreme currents exceeding 1000A per power rail, and power densities surpassing 1A/mm². Practical design examples based on the Open Compute Project’s (OCP) Open Accelerator Module (OAM) and Universal Base Board (UBB) architectures illustrate these challenges and their potential solutions. Furthermore, the talk evaluates the benefits and complexities associated with embedding technology, chiplet integration, and multi-level IVRs. Primarily forward-looking, the presentation provides insightful perspectives to inform future advancements in data center power infrastructure.

About Zhiping Yang

Zhiping Yang is the CEO of PCB Automation Inc. (https://pcbauto.ai) and an adjunct professor at Missouri S&T EMC laboratory. He worked in Waymo, Google, Apple, Cisco, and Nuova systems on automotive, consumer, and datacenter products. His research interests include signal integrity and power integrity methodology development for Die/Package/Board co-design, high-speed optical module, various high-speed cabling solutions, high-speed DRAM/storage technology, and high-speed serial signaling technology. He has published more than 70 research papers and 20 patents. His research and patents have been applied in Apple iPhone 5S/6/6S, Cisco UCS, Cisco Nexus 6K/4K/3K, and Cisco Cat6K products. He is actively involved with the IBIS Open Forum as a BoD member and officer. He is an IEEE Fellow and served the Technical Advisory Committee leadership roles in IEEE EMC society. He obtained his Ph.D. from University of Missouri-Rolla and his B.S. and M.S. from Tsinghua University, Beijing.

Jayaprakash Balachandran, d-Matrix

Santa Clara, CA, USA

Hot Topic: Engineering the Mind of Machines: Electrical Design Trends in Gen AI Processing

Abstract

With the rapid rise of Gen AI and large language models (LLMs), artificial intelligence now drives breakthroughs across industries, from productivity and healthcare to scientific discovery. However, the computational demands of LLMs are doubling every six months, far outpacing Moore’s Law and exposing a critical gap between required performance and current hardware capabilities. To address this, compute is distributed across multiple chips and systems, but this introduces significant signal and power integrity challenges. High data rates are pushing copper interconnects to their limits, while high current and transient demands strain power delivery networks. In this talk, I will discuss emerging electrical design trends shaping AI hardware for LLM processing.

About Jayaprakash Balachandran

Jayaprakash Balachandran (JP) is the Technical Director at d-Matrix, where he leads efforts in advanced packaging and system design for next-generation AI inference processing systems. Before joining d-Matrix, he worked at Cisco’s Compute Server Business Unit, contributing to the development of multiple generations of Cisco’s flagship Unified Computing System (UCS) Blade and Rack servers. Additionally, he played a key role in leading the BoW interoperability workgroup within the OCP-ODSA initiative. JP holds a Ph.D. from IMEC in Belgium.

Benjamin Dannan, Signal Edge Solutions

Baltimore, MD, USA

Power Integrity Demo: Low impedance measurements of decaps and PDN, measurements of PDN noise on active circuit

Abstract

Modern high-speed electronic systems, particularly those employing advanced ASIC and chiplet packages for AI and data center applications, face critical challenges in managing power delivery network (PDN) integrity. High current densities, coupled with higher power rail density on the package and demanding data rates, contribute to significant challenges. While PDN impedance is a key metric, measuring high-current PDNs (e.g., 2000A) presents difficulties, notably ground loop errors in 2-port measurements. Employing ground loop isolators with adequate Common-Mode Rejection Ratio (CMRR) is crucial. This presentation will demonstrate a practical approach to accurately measure a 2000-Amp (or 40 µΩ) PDN using various VNAs. We will detail how to determine the minimum CMRR needed for reliable 2-port probe measurements and show that sub-40 µΩ impedance measurements are achievable with isolators possessing sufficient CMRR.

About Benjamin Dannan

Benjamin Dannan is the Founder and Chief Technologist at Signal Edge Solutions. Benjamin Dannan is an experienced signal and power integrity (SI/PI) design consultant developing advanced packaging solutions for high-performance ASICs, chiplets, and complex FPGA designs. He is a Keysight ADS Certified Expert with expert-level proficiency in high-speed simulation solutions and multiple 3D EM solutions. He has expert-level proficiency with multiple test and measurement solutions, including oscilloscopes, vector network analyzers (VNA), Time Domain Reflectometers (TDRs), function generators, and EMC lab testing equipment.

Stefano Grivet-Talocia, Politecnico di Torino

Torino, Italy

Closing Session: Compact and surrogate models in SI/PI

Abstract

Signal and Power Integrity verification flows make extensive use of models of components, interconnects and subsystems. An accurate representation of electrical and electromagnetic system behavior often leads to extremely large, complex and impractical models, so that numerical simulations may become infeasible. Several approaches have thus been devised to automatically compress and simplify such models, through well-defined mathematical procedures termed as “macromodeling”. This talk will summarize the most relevant macromodeling methods in SI/PI, which have been proven on the field to be key enabling tools for fast simulation and verification.

About Stefano Grivet-Talocia

Stefano Grivet-Talocia (Fellow, IEEE) is currently a Full Professor of Electrical Engineering with the Politecnico di Torino, Italy. He authored more than 200 international refereed publications in the field of passive macromodeling of lumped and distributed interconnect structures for Signal/Power Integrity, model order reduction, modeling and simulation of fields, circuits, and their interaction. He is part of the top 2% worldwide researcher catalog (Stanford) since 2019. He currently serves as AE for the IEEE Trans. CPMT. He was co-founder (2007) and President of the academic Spin-off IdemWorks, until acquisition by CST in 2016.